Why is this happening?

This is sine table .align 9 to align it to the cache line size (64 bytes according to Cortex A53 manual)Disassembly:![Image]()

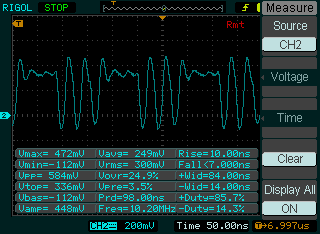

Moved sine table to 0x10000 and padded with zeros and original location three different waveforms?

This is sine table .align 9 to align it to the cache line size (64 bytes according to Cortex A53 manual)

Code:

* same fiq code *.align 9SineTable:.word 0x28282726...SineTableEnd:Code:

0000801c <_fiq_start>: 801c: e3a0c301 mov ip, #67108864 ; 0x4000000 ... 8054: e25ef004 subs pc, lr, #4 8058: e1a00000 nop ...00008200 <SineTable>: 8200: 28282726 .word 0x28282726

Moved sine table to 0x10000 and padded with zeros and original location three different waveforms?

https://developer.arm.com/documentation ... -directiveUse ALIGN with a coarser setting to take advantage of caches on some ARM processors. For example, the ARM940T has a cache with 4-word lines. Use ALIGN 16 to align function entries on 16-byte boundaries and maximize the efficiency of the cache.

Statistics: Posted by MaximBondaruk — Sat Apr 06, 2024 9:21 am